Rev D1, Page 1/45

#### **FEATURES**

- ♦ System-on-chip design for excellent reliability

- ♦ Leading/trailing sampling of 10 binary tracks pitched at 400 µm

- ♦ Analog sine/cosine scanning with enlarged photodiodes, signal conditioning and fast 8-bit vector-tracking interpolation

- ♦ Absolute singleturn resolution up to 18 bits

- ◆ FlexCount<sup>®</sup> provides programmable resolution for absolute and incremental data

- Incremental quadrature outputs with 1 to 65,536 CPR and programmable index signal

- ◆ LED illumination control using 50 mA high-side current source (sin²+cos² or sum control modes)

- ♦ Alarm indication for configuration or illumination error

- ♦ Permanent RAM monitoring by parity bits

- ♦ 3.3 V-compatible SPI and I/O ports for configuration and data

- ♦ Serial position readout in 1 µs cycles at 16 MHz clock frequency

- ♦ Parallel position output resolution up to 16 bits

- ♦ Operation at 4 V to 5.5 V within -40 °C to 110 °C

- ♦ 30-pin optoBGA or 38-pin optoQFN package for SMT

- ♦ Illumination: iC-SN85 BLCC SN1C (850 nm encoder LED)

- ♦ Code discs: LNB1S 42-1024 (1024 PPR, Ø 42 mm/18 mm), LNB4S 26-1024 (1024 PPR, Ø 26 mm/9.6 mm)

#### **APPLICATIONS**

- Programmable incremental encoders

- Optical position sensors

- ♦ Absolute rotary encoders

- ♦ Motor feedback systems

- Linear scales

Rev D1, Page 2/45

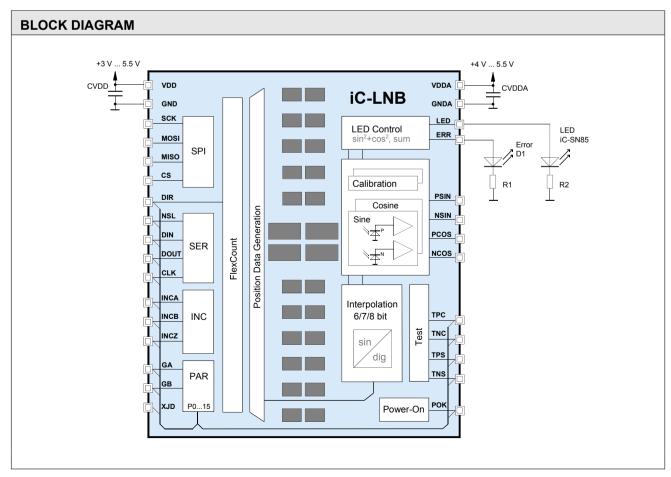

#### **DESCRIPTION**

The iC-LNB is an optoelectronic encoder IC for absolute linear and angle measuring systems. When combined with a linear scale or rotary encoder disc, the iC-LNB provides complete encoder functionality. Photodiodes, amplifiers, comparators, a complete signal conditioning unit, and multiple interfaces for position data output are monolithically integrated into the device.

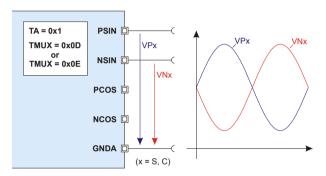

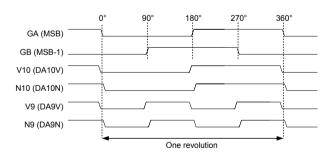

The iC-LNB reads ten absolute tracks as well as an incremental track from the disc or scale. The incremental track provides sine and cosine signals which can be calibrated to compensate the offset and scale the amplitude of the photodiodes. These calibrated signals are used by the integrated vector-tracking interpolator to provide up to 8 bits of additional resolution and are also available on dedicated output pins. Combined with the 10 bits of absolute position, the interpolator provides resolution of up to 18 bits.

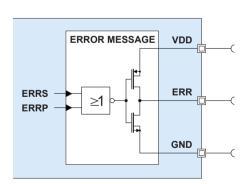

An integrated LED current control with a built-in driver allows direct connection of the illumination LED (iC-SN85 or other). The optical power received by the iC-LNB is kept constant by the current control, regardless of temperature and aging effects of the LED. The received power setpoint is programmable and an end-of-life alarm and error pin output indicate when the LED current control has exceeded its operating range.

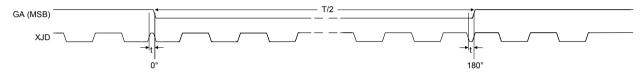

The iC-LNB synchronizes the interpolator output and the absolute data to form a contiguous Gray-coded position data word. This position or angle data is output as incremental ABZ signals, absolute position via a scalable shift-register, and through the SPI interface. Alternatively, a 16-bit parallel position output is also available. FlexCount<sup>®</sup> allows the output position (incremental and absolute) resolution to be programmed to any value between 4 and 2<sup>18</sup> steps (edges) per revolution.

After startup, the iC-LNB must be configured via the SPI interface. The SPI interface (as well as all the other digital I/O) operates at 3.3 V, allowing direct connection to 3.3 V microcontrollers.

#### General notice on application-specific programming

Parameters defined in the datasheet represent supplier's attentive tests and validations, but - by principle - do not imply any warranty or guarantee as to their accuracy, completeness or correctness under all application conditions. In particular, setup conditions, register settings and power-up have to be thoroughly validated by the user within his specific application environment and requirements (system responsibility).

The chip's performance in application is impacted by system conditions like the quality of the optical target, the illumination, temperature and mechanical stress, sensor alignment and initial calibration.

Rev D1, Page 3/45

### **CONTENTS**

| PACKAGING INFORMATION                            | 4  | Enable/Disable                         | 29              |

|--------------------------------------------------|----|----------------------------------------|-----------------|

| PIN CONFIGURATION                                |    | Incremental FlexCount Output           |                 |

| oBGA LNB2C                                       |    | Absolute FlexCount Output              | 29              |

| (7.6 mm x 7.1 mm x 1.6 mm)                       | 4  | Resolution                             | 29              |

| PIN CONFIGURATION                                |    | Position offset                        | 30              |

| oQFN38-7x5                                       |    | Absolute Position Numeric Formats      | 30              |

| (7.0 mm x 5.0 mm x 0.9 mm)<br>(in qualification) | 5  | Changing FlexCount Resolution, Offset, | 00              |

| PAD LAYOUT                                       | 6  | or Direction                           | 30              |

|                                                  | -  | 0.2.00.0                               |                 |

| PACKAGE DIMENSIONS oQFN38-7x5                    | 7  | OPERATING MODE                         | 32              |

| ABSOLUTE MAXIMUM RATINGS                         | 8  | Interface Mode                         | 32              |

|                                                  |    | Parallel Mode                          | 32              |

| THERMAL DATA                                     | 8  |                                        |                 |

| ELECTRICAL CHARACTERISTICS                       | •  | INCREMENTAL (ABZ) OUTPUTS              | 33              |

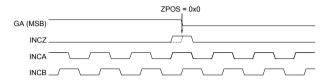

| ELECTRICAL CHARACTERISTICS                       | 9  | ABZ Resolution                         | 33              |

| OPERATING REQUIREMENTS                           | 15 | Direction Reversal                     | 33              |

| SPI Interface                                    | 15 | Incremental Output Inversion           | 33              |

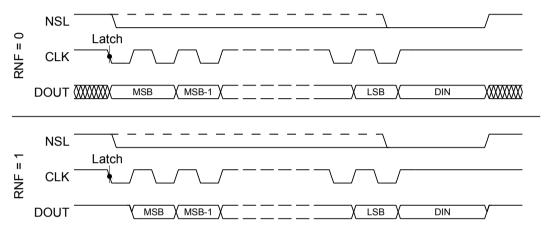

| Shift Register                                   | 16 | INCZ Position                          | 33              |

| Stillt Register                                  | 10 | INCZ Width                             | 34              |

| CONFIGURATION PARAMETERS                         | 17 | Tristate                               | 34              |

| CONFIGURING THE IC-LNB                           | 18 | SHIFT REGISTER OUTPUT                  | 35              |

| Address Range                                    | 18 | Output Data Length                     | 35              |

| RAM Monitoring (parity check)                    | 18 | Output Data Format                     | 35              |

|                                                  | 18 | Idle Output                            | 35              |

| Chip Version                                     |    | Direction Reversal                     | 36              |

| Reset Values                                     | 19 | Shift Register Disable                 |                 |

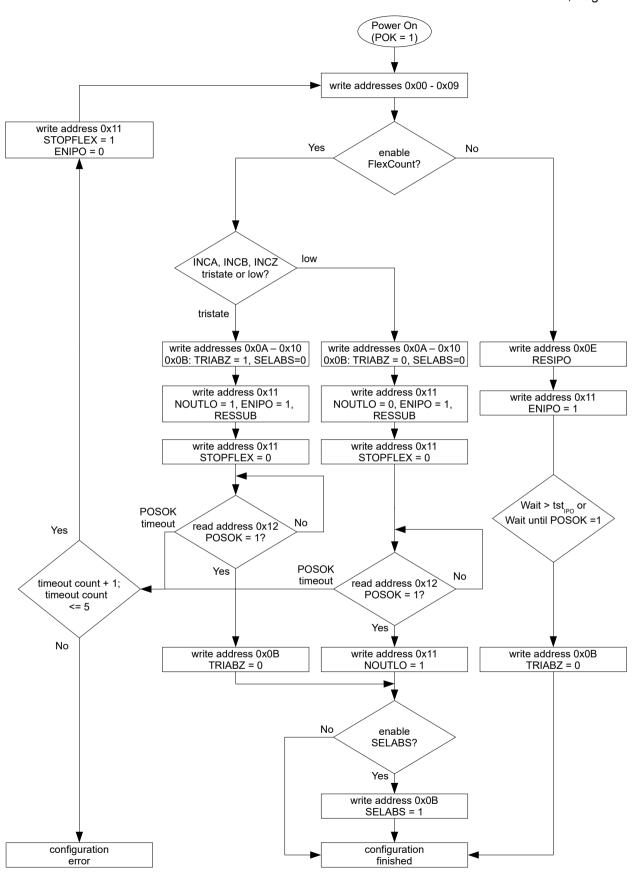

| Programming Sequence                             | 19 |                                        |                 |

| SPI INTERFACE                                    | 21 | GRAY CODE OUTPUTS                      | 36              |

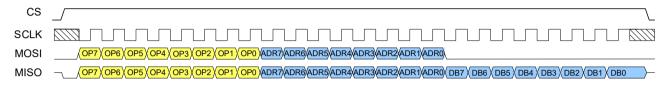

| General Protocol Description                     | 21 | PARALLEL OUTPUT MODE                   | 37              |

| Opcodes                                          | 21 |                                        | •               |

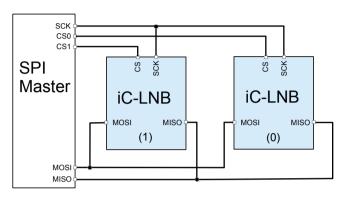

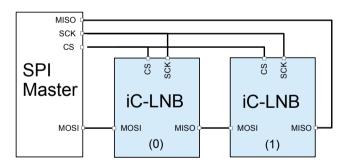

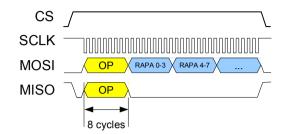

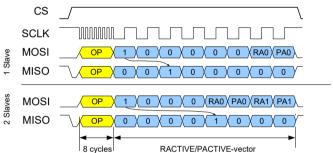

| Bussing and Chaining Multiple iC-LNBs            | 25 | ADJUSTMENTS                            | 38              |

|                                                  |    | Tilt Angle                             | 38              |

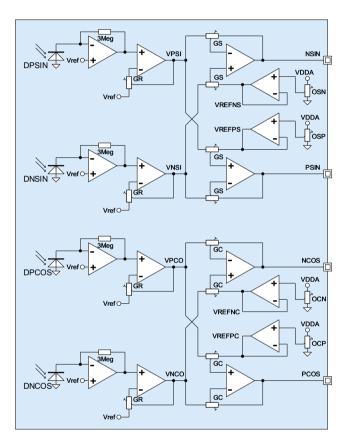

| SIGNAL CONDITIONING                              | 26 | Radial Position                        | 38              |

| Gain Range (GR)                                  | 26 |                                        |                 |

| Sine Gain (GS) and Offsets (OSP and OSN)         | 26 | LED POWER CONTROL                      | 39              |

| Cosine Gain (GC) and Offsets (OCP and OCN)       | 27 | AL ADM CUTDUT                          | -00             |

| LED Power Control                                | 27 | ALARM OUTPUT                           | 39              |

| INTERPOLATOR                                     | 28 | OSCILLATOR                             | 40              |

| Interpolator Resolution                          | 28 | TEST FUNCTIONS                         | 41              |

| Interpolator Hysteresis                          | 28 | 12011000000                            | <del>-+</del> 1 |

| Interpolator Filter                              | 28 | DESIGN REVIEW: Notes On Chip Functions | 42              |

| FLEXCOUNT®                                       | 29 | REVISION HISTORY                       | 43              |

Rev D1, Page 4/45

#### **PACKAGING INFORMATION**

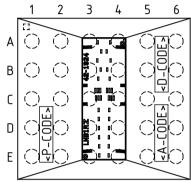

**PIN CONFIGURATION** oBGA LNB2C  $(7.6 \, \text{mm} \, \text{x} \, 7.1 \, \text{mm} \, \text{x} \, 1.6 \, \text{mm})$

B3 MOSI SPI Data Input

B5 NSIN **B6 PSIN**

Analog Voltage Output NSIN

Analog Voltage Output PSIN

B4 PCOS Analog Voltage Output PCOS

|     | В     |                                   | •  | •    | Parallel Output Bit 1                    |

|-----|-------|-----------------------------------|----|------|------------------------------------------|

|     |       |                                   | C5 | TPC  | Test Input PCOS /                        |

|     | C     |                                   |    |      | Parallel Output Bit 0                    |

|     |       |                                   | C6 | NCOS | Analog Voltage Output NCOS               |

|     | D     | 이렇이 <b>!!!이</b> 이렇이               | D1 |      | Shift Register Data Output /             |

|     | _     |                                   |    |      | Parallel Output Bit 10                   |

|     | E     |                                   | D2 | DIN  | Shift Register Data Input /              |

|     |       |                                   |    |      | Parallel Output Bit 11                   |

|     |       |                                   | D3 | NSL  | Shift Register Load Input (active low) / |

|     |       |                                   |    |      | Parallel Output Bit 12                   |

|     |       |                                   | D4 | INCB | Incremental Output B /                   |

|     |       |                                   |    |      | Parallel Output Bit 3                    |

|     |       |                                   | D5 | INCA | Incremental Output A /                   |

| PIN | FUNCT | IONS                              |    |      | Parallel Output Bit 2                    |

| No. | Name  | Function                          | D6 | ERR  | Error Message Output (active high)       |

| Α1  | SCLK  | SPI Clock Input                   | E1 | GB   | Gray Code Output B (MSB-1) /             |

| A2  | VDD   | +3V+5.5V I/O Ports Supply Voltage |    |      | Parallel Output Bit 7                    |

|     |       | I/O Ports Ground                  | E2 | GA   | Gray Code Output A (MSB) /               |

| A4  | LED   | LED High-Side Current Source      |    |      | Parallel Output Bit 8                    |

| A5  | VDDA  | +4V+5.5V Supply Voltage           | E3 | CLK  | Shift Register Clock Input /             |

|     |       | Ground                            |    |      | Parallel Output Bit 9                    |

|     | CS    | SPI Chip Select Input             | E4 | XJD  | Adjustment Signal /                      |

| B2  | MISO  | SPI Data Output                   |    |      | Parallel Output Bit 6                    |

Power OK Indication/

Parallel Output Bit 5

Incremental Output Z /

Parallel Output Bit 4

**PIN FUNCTIONS**

C1 DIR

C2 TNS

C3 TNC

C4 TPS

E5 POK

E6 INCZ

No. Name Function

Code Inversion Input / Parallel Output Bit 13

Test Input NSIN / Parallel Output Bit 14

Test Input NCOS / Parallel Output Bit 15

Test Input PSIN /

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes); Grounding unused inputs (10 kΩ to GNDA) is recommended, especially for pins DIR, TPS, TNS, TPC, and TNC. For dimensional specifications, refer to package datasheet iC-LNB oBGA LNB2C, available separately.

Rev D1, Page 5/45

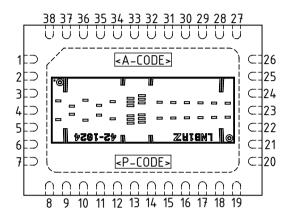

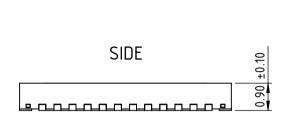

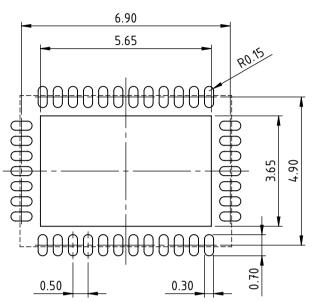

### PIN CONFIGURATION oQFN38-7x5 (7.0 mm x 5.0 mm x 0.9 mm) (in qualification)

#### **PIN FUNCTIONS**

| PIN | FUNCI             | IONS                              |

|-----|-------------------|-----------------------------------|

| No. | Name              | Function                          |

| 1   | <b>GNDA</b>       | Ground                            |

| 2-6 | n.c. <sup>1</sup> | Not Connected                     |

| 7   | GND               | I/O Ports Ground                  |

| 8   | VDD               | +3V+5.5V I/O Ports Supply Voltage |

| 9   | SCLK              | SPI Clock Input                   |

| 10  | MOSI              | SPI Data Input                    |

| 11  | MISO              | SPI Data Output                   |

| 12  | CS                | SPI Chip Select Input             |

| 13  | TNC               | Test Input NCOS /                 |

|     |                   | Parallel Output Bit 15            |

| 14  | TNS               | Test Input NSIN /                 |

|     |                   | Parallel Output Bit 14            |

| 15  | DIR               | Code Inversion Input /            |

|     |                   | Parallel Output Bit 13            |

#### **PIN FUNCTIONS**

BP<sup>2</sup>

Name Function

| 16    | NSL               | Shift Register Load Input (active low) / Parallel Output Bit 12 |

|-------|-------------------|-----------------------------------------------------------------|

| 17    | DIN               | Shift Register Data Input /                                     |

| 40    | DOLLT             | Parallel Output Bit 11                                          |

| 18    | DOUT              | Shift Register Data Output / Parallel Output Bit 10             |

| 10    | CLK               | Shift Register Clock Input /                                    |

| 13    | OLIV              | Parallel Output Bit 9                                           |

| 20    | GB                | Gray Code Output B (MSB-1) /                                    |

|       | -                 | Parallel Output Bit 7                                           |

| 21    | GA                | Gray Code Output A (MSB) /                                      |

|       |                   | Parallel Output Bit 8                                           |

| 22-24 | n.c. <sup>1</sup> | Not Connected                                                   |

| 25    | POK               | Power OK Indication/                                            |

|       |                   | Parallel Output Bit 5                                           |

| 26    | XJD               | Adjustment Signal /                                             |

|       |                   | Parallel Output Bit 6                                           |

| 27    | INCZ              | Incremental Output Z /                                          |

| 20    | INICD             | Parallel Output Bit 4                                           |

| 28    | INCB              | Incremental Output B / Parallel Output Bit 3                    |

| 29    | INCA              | Incremental Output A /                                          |

| 23    | INOA              | Parallel Output Bit 2                                           |

| 30    | ERR               | Error Message Output (active high)                              |

|       | TPS               | Test Input PSIN /                                               |

|       |                   | Parallel Output Bit 1                                           |

| 32    | TPC               | Test Input PCOS /                                               |

|       |                   | Parallel Output Bit 0                                           |

|       | NCOS              | 3 3 1                                                           |

|       | PCOS              | Analog Voltage Output PCOS                                      |

|       | NSIN              | Analog Voltage Output NSIN                                      |

|       | PSIN              | Analog Voltage Output PSIN                                      |

|       | LED               | LED High-Side Current Source                                    |

| აგ    | VDDA              | +4V+5.5V Supply Voltage                                         |

|       |                   |                                                                 |

Backside paddle

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes); Grounding unused inputs (10 k $\Omega$  to GNDA) is recommended, especially for pins DIR, TPS, TNS, TPC, and TNC.

<sup>&</sup>lt;sup>1</sup> Pin numbers marked n.c. are not connected.

<sup>&</sup>lt;sup>2</sup> Connecting the backside paddle is recommended by a single link to GNDA. A current flow across the paddle is not permissible.

Rev D1, Page 6/45

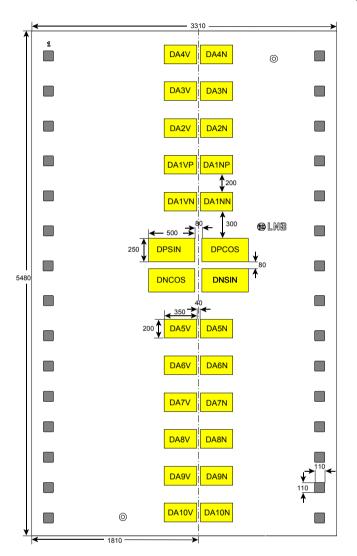

### **PAD LAYOUT**

### PAD FUNCTIONS

|    | Name        | Function                                                        |

|----|-------------|-----------------------------------------------------------------|

| 1  | GND         | I/O Ports Ground                                                |

|    | VDD         | +3 V +5.5 V I/O Ports Supply Voltage                            |

|    | SCLK        | SPI Clock Input                                                 |

|    | MOSI        | SPI Data Input                                                  |

|    | MISO        | SPI Data Output                                                 |

|    | CS          | SPI Chip Select Input                                           |

| 7  | TNC         | Test Input NCOS /                                               |

| _  |             | Parallel Output Bit 15                                          |

| 8  | TNS         | Test Input NSIN /                                               |

| ^  | DID         | Parallel Output Bit 14                                          |

| 9  | DIR         | Code Inversion Input /                                          |

| 10 | NCI         | Parallel Output Bit 13                                          |

| 10 | NSL         | Shift Register Load Input (active low) / Parallel Output Bit 12 |

| 11 | DIN         | Shift Register Data Input /                                     |

|    | DIN         | Parallel Output Bit 11                                          |

| 12 | DOUT        | Shift Register Data Output /                                    |

|    | 500.        | Parallel Output Bit 10                                          |

| 13 | CLK         | Shift Register Clock Input /                                    |

|    |             | Parallel Output Bit 9                                           |

| 14 | GA          | Gray Code Output A (MSB) /                                      |

|    |             | Parallel Output Bit 8                                           |

| 15 | GB          | Gray Code Output B (MSB-1) /                                    |

|    |             | Parallel Output Bit 7                                           |

| 16 | XJD         | Adjustment Signal /                                             |

|    |             | Parallel Output Bit 6                                           |

| 17 | POK         | Power OK Indication/                                            |

| 40 | 11107       | Parallel Output Bit 5                                           |

| 18 | INCZ        | Incremental Output Z /                                          |

| 10 | INICD       | Parallel Output Bit 4                                           |

| 19 | INCB        | Incremental Output B / Parallel Output Bit 3                    |

| 20 | INCA        | Incremental Output A /                                          |

| 20 | INCA        | Parallel Output Bit 2                                           |

| 21 | ERR         | Error Message Output (active high)                              |

|    | TPS         | Test Input PSIN /                                               |

|    | 0           | Parallel Output Bit 1                                           |

| 23 | TPC         | Test Input PCOS /                                               |

| _  |             | Parallel Output Bit 0                                           |

| 24 | NCOS        | Analog Voltage Output NCOS                                      |

| 25 | <b>PCOS</b> | Analog Voltage Output PCOS                                      |

| 26 | NSIN        | Analog Voltage Output NSIN                                      |

| 27 | PSIN        | Analog Voltage Output PSIN                                      |

| 28 | LED         | LED High-Side Current Source                                    |

29 VDDA +4V...+5.5V Supply Voltage

30 GNDA Ground

Grounding unused inputs (10 k $\Omega$  to GNDA) is recommended, especially for pins DIR, TPS, TNS, TPC, and TNC.

Rev D1, Page 7/45

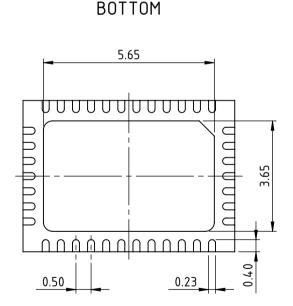

#### **PACKAGE DIMENSIONS oQFN38-7x5**

### RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm. Tolerances of form and position according to JEDEC M0–220. Positional tolerance of reticle pattern:  $\pm 90 \mu \text{m}$  /  $\pm 1^{\circ}$  (with respect to center of backside pad). G4: radius of chip center (refer to the relevant encoder disc and code description). Maximum molding excess  $\pm 20 \mu \text{m}$  /  $\pm 75 \mu \text{m}$  versus surface of glass/reticle.

drd\_lnb-oqfn38-1\_pack\_1, 8:1

Rev D1, Page 8/45

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply permissible operating conditions; functional operation is not guaranteed. Exceeding these ratings may damage the device.

| Item | Symbol  | Parameter                                                                                                                      | Conditions                          |      |          | Unit |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|----------|------|

| No.  |         |                                                                                                                                |                                     | Min. | Max.     |      |

| G001 | VDDA    | Voltage at VDDA                                                                                                                |                                     | -0.3 | 6        | V    |

| G002 | VDD     | Voltage at VDD                                                                                                                 |                                     | -0.3 | VDDA+0.3 | V    |

| G003 | V(GND)  | Voltage at GND                                                                                                                 |                                     | -0.3 | 0.3      | V    |

| G004 | V()     | Voltage at LED, PCOS, NCOS, PSIN, NSIN, TPC, TNC, TPS, TNS                                                                     |                                     | -0.3 | VDDA+0.3 | V    |

| G005 | V()     | Voltage at INCA, INCB, INCZ, ERR,<br>DIR, CLK, DOUT, DIN, NSL, CS, MOSI,<br>MISO, SCK, POK, XJD, GA, GB                        | ,                                   | -0.3 | VDD+0.3  | V    |

| G006 | I(VDDA) | Current in VDDA                                                                                                                |                                     | -100 | 100      | mA   |

| G007 | I(VDD)  | Current in VDD                                                                                                                 |                                     | -50  | 50       | mA   |

| G008 | I(GND)  | Current in GND                                                                                                                 |                                     | -20  | 20       | mA   |

| G009 | I(LED)  | Current in LED                                                                                                                 |                                     | -100 | 20       | mA   |

| G010 | I()     | Current in INCA, INCB, INCZ, ERR,<br>DIR, CLK, DOUT, DIN, NSL, CS, MOSI,<br>MISO, SCK, POK, XJD, GA, GB, TPC,<br>TNC, TPS, TNS | ,                                   | -35  | 35       | mA   |

| G011 | I()     | Current in PCOS, NCOS, PSIN, NSIN                                                                                              |                                     | -35  | 35       | mA   |

| G012 | Vd()    | ESD Susceptibility at all pins                                                                                                 | HBM 100pF discharged through 1.5 kΩ |      | 2        | kV   |

| G013 | Tj      | Junction Temperature                                                                                                           |                                     | -40  | 125      | °C   |

| G014 | Ts      | Chip Storage Temperature                                                                                                       |                                     | -40  | 125      | °C   |

### THERMAL DATA

Operating conditions: VDDA = 4 V to 5.5 V, VDD = 3 V to 5.5 V, GNDA = GND

| Item | Symbol | Parameter                             | Conditions                                                                                            |      |      | .,         | Unit |

|------|--------|---------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------------|------|

| No.  |        |                                       |                                                                                                       | Min. | Тур. | Max.       |      |

| T01  | Та     | Operating Ambient Temperature Range   | packages oBGA LNB2C, oQFN38-7x5                                                                       | -40  |      | 110        | °C   |

| T02  | Ts     | Permissible Storage Temperature Range | packages oBGA LNB2C, oQFN38-7x5                                                                       | -40  |      | 110        | °C   |

| T03  | Tpk    | Soldering Peak Temperature            | package oBGA LSH2C                                                                                    |      |      |            |      |

|      |        |                                       | tpk < 20 s, convection reflow<br>tpk < 20 s, vapor phase soldering                                    |      |      | 245<br>230 | °C   |

|      |        |                                       | TOL (time on label) 8 h;<br>Please refer to customer information file No. 7<br>for details.           |      |      |            |      |

| T04  | Tpk    | Soldering Peak Temperature            | package oQFN38-7x5                                                                                    |      |      |            |      |

|      |        |                                       | tpk < 20 s, convection reflow<br>tpk < 20 s, vapor phase soldering                                    |      |      | 245<br>230 | °C   |

|      |        |                                       | MSL 5A (max. floor life 24 h at 30 °C and 60% RH);<br>Please refer to customer information file No. 7 |      |      |            |      |

|      |        |                                       | for details.                                                                                          |      |      |            |      |

Rev D1, Page 9/45

### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol             | Parameter                                                                                                                   | Conditions                                           | Min.                      | Тур.                  | Max.                       | Unit            |

|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|-----------------------|----------------------------|-----------------|

| Total       | Device             |                                                                                                                             | I                                                    | Ш                         |                       | ļ                          |                 |

| 001         | VDDA               | Permissible Supply Voltage                                                                                                  |                                                      | 4                         | 5                     | 5.5                        | V               |

| 002         | VDD                | Permissible I/O Supply Voltage                                                                                              | VDD < VDDA                                           | 3                         | 5                     | 5.5                        | V               |

| 003         | VDDA,<br>VDD       |                                                                                                                             | at 150 kHz                                           |                           | 10                    |                            | mV              |

| 004         | I(VDDA),<br>I(VDD) | Supply Current in VDDA and VDD (sum)                                                                                        | without currents I(LED) and I(ERR), Tj = 27 °C       |                           | 25                    | 40                         | mA              |

| 005         | Vcz()hi            | Clamp Voltage hi at all Pins                                                                                                | I() = 4 mA                                           |                           |                       | 11                         | V               |

| 006         | Vc()hi             | Clamp Voltage hi at<br>CLK, DIN, NSL, INCA, INCB,<br>INCZ, ERR, DIR, MISO, DOUT,<br>POK, XJD, GA, GB, TPS, TNS,<br>TPC, TNC | Vc()hi = V() — V(VDD),<br>I() = 4 mA                 | 0.3                       |                       | 1.2                        | V               |

| 007         | Vc()hi             | Clamp Voltage hi at CS, MOSI, SCK                                                                                           | Vc()hi = V() — V(VDD),<br>I() = 4 mA                 | 1.2                       |                       | 2.2                        | V               |

| 800         | Vc()lo             | Clamp Voltage lo at all Pins                                                                                                | I() = -4 mA                                          | -1.2                      |                       | -0.3                       | V               |

| 009         | CVDDA,<br>CVDD     | Required Backup Capacitors at VDDA, VDD                                                                                     | placed near by pin, recommended low ESR              |                           | 1                     |                            | μF              |

| Photo       | diodes             |                                                                                                                             |                                                      |                           |                       |                            |                 |

| 101         | $Se(\lambda)$      | Spectral Application Range                                                                                                  | $Se(\lambda) = 0.25 \times S(\lambda) max$           | 400                       |                       | 950                        | nm              |

| 102         | S(λ)max            | Spectral Sensitivity                                                                                                        | $\lambda$ = 690 nm                                   |                           | 0.45                  |                            | A/W             |

| 103         | $S(\lambda)$       | Spectral Sensitivity                                                                                                        | $\lambda$ = 850 nm                                   |                           | 0.30                  |                            | A/W             |

| 104         | Aph()              | Radiant Sensitive Area DPSIN, DNSIN, DPCOS, DNCOS                                                                           | 0.5 mm x 0.25 mm                                     |                           | 0.125                 |                            | mm <sup>2</sup> |

| 105         | Aph()              | Radiant Sensitive Area Digital<br>DA1VP, DA1VN, DA1NP, DA1NN,<br>DA2V DA10V, DA2N DA10N                                     | 0.35 mm x 0.2 mm                                     |                           | 0.07                  |                            | mm <sup>2</sup> |

| Photo       | current Am         | plifier                                                                                                                     |                                                      |                           |                       |                            |                 |

| 201         | lph()              | Permissible Photocurrent<br>Operating Range                                                                                 |                                                      | 0                         |                       | 200                        | nA              |

| 202         | Z()                | Equivalent Transimpedance Gain                                                                                              | Z() = Vout() / lph()                                 | 1.8                       | 3.0                   | 4.2                        | MΩ              |

| 203         | ∆Z()pn             | Transimpedance Gain Matching of an Amplifier Pair                                                                           | P-channel versus corresponding N-channel             | -0.2                      |                       | 0.2                        | %               |

| 204         | fhc()              | Upper Cut-off Frequency (-3 dB)                                                                                             | without LED current control                          | 120                       | 300                   | 500                        | kHz             |

| 205         | VR()               | Ratio of Reference Voltage Digital Tracks (Vcomp) to Sum of Digital Track 1                                                 | $VR() = \frac{Vcomp}{VA1VP + VA1VN + VA1NP + VA1NN}$ |                           | 0.25                  |                            |                 |

| 206         | Hys()              | Hysteresis Digital Tracks                                                                                                   |                                                      | 5                         | 15                    | 25                         | mV              |

| 207         | GR()               | Coarse Gain Range Analog Track                                                                                              | GR = 0x00<br>GR = 0x01<br>GR = 0x02<br>GR = 0x03     | 0.9<br>1.2<br>1.45<br>1.8 | 1<br>1.33<br>1.6<br>2 | 1.1<br>1.45<br>1.75<br>2.2 |                 |

| 208         | Vref               | Reference Voltage of Photocur-<br>rent Amplifiers                                                                           |                                                      | 0.6                       | 0.8                   | 1                          | V               |

| 209         | ∆Vd()sc            | Analog Track Dark Signal Voltage versus Vref                                                                                | ΔVd()sc = V() - Vref                                 | -20                       |                       | 20                         | mV              |

| 210         | △Vd()dig           | Digital Tracks Dark Signal Voltage versus Vref                                                                              | $\Delta Vd()dig = V() - Vref$                        | -35                       |                       | 35                         | mV              |

Rev D1, Page 10/45

### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol            | Parameter                                 | Conditions                                                                                                                                                                                                   | Min. | Тур.                             | Max.                      | Unit                     |

|-------------|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|---------------------------|--------------------------|

| Signa       | l Condition       | ing Sin/Cos                               |                                                                                                                                                                                                              |      |                                  |                           | .11                      |

| 301         | Gmin              | Adjustable Minimum Gain                   | GS, GC = 0x00                                                                                                                                                                                                |      | 1                                |                           |                          |

| 302         | Gmax              | Adjustable Maximum Gain                   | GS, GC = 0x3F                                                                                                                                                                                                |      | 2                                |                           |                          |

| 303         | ∆Gdiff            | Differential Gain Calibration<br>Accuracy | calibration range 6 bit                                                                                                                                                                                      | -0.5 |                                  | 0.5                       | LSB                      |

| 304         | Omin              | Offset Calibration Min                    | OSP, OSN, OCP, OCN = 0x00                                                                                                                                                                                    | 45   | 47.5                             | 50                        | %VDDA                    |

| 305         | Omax              | Offset Calibration Max                    | OSP, OSN, OCP, OCN = 0x7F                                                                                                                                                                                    | 50   | 52.5                             | 55                        | %VDDA                    |

| 306         | ∆Odiff            | Differential Offset Calibration Accuracy  | calibration range 7 bit                                                                                                                                                                                      | 0.01 | 0.04                             | 0.06                      | %VDDA                    |

| Outpu       | ıt Voltage P      | SIN, NSIN, PCOS, NCOS                     |                                                                                                                                                                                                              |      |                                  |                           |                          |

| 401         | Vdc()             | DC-Voltage at all Outputs                 | Offset adjusted to VDDA/2                                                                                                                                                                                    | 47   | 50                               | 53                        | %VDDA                    |

| 402         | Vpk()             | Permissible Signal Amplitude              | DC level = VDDA/2                                                                                                                                                                                            |      | 0.5                              | 0.6                       | V                        |

| 403         | I()mx             | Permissible Output Current                |                                                                                                                                                                                                              | -1   |                                  | 1                         | mA                       |

| 404         | Ri()              | Output Resistor                           | I() = -1 1 mA                                                                                                                                                                                                |      | 75                               | 200                       | Ω                        |

| LED P       | ower Cont         | rol LED, Error Message ERR                |                                                                                                                                                                                                              |      |                                  |                           |                          |

| 501         | lmx()             | Permissible LED Current at LED            |                                                                                                                                                                                                              | -100 |                                  | 0                         | mA                       |

| 502         | lop()             | LED Current Control Range                 | ERRS (internal) = 0, V(LED) > Vs(LED)                                                                                                                                                                        | -50  |                                  | -1                        | mA                       |

| 503         | Vs()              | Saturation Voltage at LED                 | Vs() = VDDA - V(LED); I() = -50 mA                                                                                                                                                                           |      |                                  | 1                         | V                        |

| 504         | tr()              | Rise Time LED Current                     | I(LED): 0 % → 90 %                                                                                                                                                                                           |      | 0.8                              | 1.5                       | ms                       |

| 505         | tset()            | Settling Time of LED Control<br>Loop      | amplitude at PSIN, NSIN, PCOS and NCOS from 50 % to 100 % of setpoint                                                                                                                                        |      | 300                              |                           | μs                       |

| 506         | Vs()hi            | Saturation Voltage hi at ERR              | Vs()hi = VDD - V(ERR);<br>VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                                                                                                                           |      |                                  | 400                       | mV                       |

| 507         | Isc()hi           | Short-Circuit Current hi at ERR           |                                                                                                                                                                                                              | -100 |                                  | -1.5                      | mA                       |

| 508         | Vs()lo            | Saturation Voltage Io at ERR              | VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                                                                                                                                                     |      |                                  | 400                       | mV                       |

| 509         | lsc()lo           | Short-Circuit Current lo at ERR           |                                                                                                                                                                                                              | 1.5  |                                  | 100                       | mA                       |

| Interp      | olator            |                                           |                                                                                                                                                                                                              |      |                                  |                           |                          |

| 701         | AAabs             | Absolute Angular Position<br>Accuracy     | referenced to Sin/Cos signal period, HYS = 0x00 RESIPO = 11 (5 bit interpolation) RESIPO = 10 (6 bit interpolation) RESIPO = 01 (7 bit interpolation) RESIPO = 00 (8 bit interpolation)                      |      | ± 7.0<br>± 4.2<br>± 2.8<br>± 1.4 |                           | DEG<br>DEG<br>DEG<br>DEG |

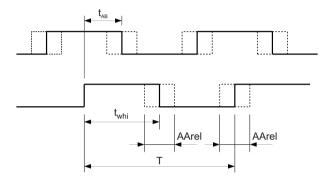

| 702         | AArel             | Relative Angular Error                    | referenced to output period T, see Figure 1 RESIPO = 11 (5 bit interpolation) RESIPO = 10 (6 bit interpolation) RESIPO = 01 (7 bit interpolation) RESIPO = 00 (8 bit interpolation)                          |      | 1<br>2<br>4<br>8                 |                           | %<br>%<br>%<br>%         |

| 703         | AAhys             | Angular Hysteresis                        | referenced to output period T, see Figure 1 and Table 25, HYS = 0x00 RESIPO = 11 (5 bit interpolation) RESIPO = 10 (6 bit interpolation) RESIPO = 01 (7 bit interpolation) RESIPO = 00 (8 bit interpolation) |      | ± 1.4<br>± 1.4<br>± 1.4<br>± 0.7 |                           | DEG<br>DEG<br>DEG<br>DEG |

| 704         | tw()hi            | Duty Cycle                                | referenced to output period T, see Figure 1                                                                                                                                                                  |      | 50                               |                           | %                        |

| 705         | t <sub>AB</sub>   | Phase Shift A versus B                    | referenced to output period T, see Figure 1                                                                                                                                                                  |      | 25                               |                           | %                        |

| 706         | f <sub>max</sub>  | Maximum Permissible Sin/Cos<br>Frequency  | OSZC = 10 RESIPO = 11 (5 bit interpolation) RESIPO = 10 (6 bit interpolation) RESIPO = 01 (7 bit interpolation) RESIPO = 00 (8 bit interpolation)                                                            |      |                                  | 250<br>226<br>113<br>56.5 | kHz<br>kHz<br>kHz<br>kHz |

| 707         | tp <sub>IPO</sub> | Propagation Delay Interpolator            |                                                                                                                                                                                                              |      |                                  | 1/f <sub>oipo</sub>       |                          |

Rev D1, Page 11/45

### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol                | Parameter                                      | Conditions                                                                                                                                                                                            | Min.  | Тур. | Max.                       | Unit                     |

|-------------|-----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|----------------------------|--------------------------|

| 708         | tst <sub>IPO</sub>    | Startup Time Interpolator                      | OSZC = 10, SELABS = 1, no illumination error, until POSOK = 1 RESIPO = 11 (5 bit interpolation): startup at 14500 rpm startup at standstill RESIPO = 10 (6 bit interpolation): startup at 13200 rpm   | NIII. | тур. | 5<br>2<br>600              | μs<br>μs<br>μs           |

|             |                       |                                                | startup at 12000 rpm<br>startup at standstill<br>RESIPO = 01 (7 bit interpolation):                                                                                                                   |       |      | 30<br>4                    | μs<br>μs                 |

|             |                       |                                                | startup at 6600 rpm<br>startup at 6000 rpm<br>startup at standstill<br>RESIPO = 00 (8 bit interpolation):<br>startup at 3300 rpm                                                                      |       |      | 1100<br>55<br>6<br>2000    | µs<br>µs<br>µs           |

|             |                       |                                                | startup at 3000 rpm<br>startup at standstill                                                                                                                                                          |       |      | 100<br>10                  | μs<br>μs                 |

| FlexC       | ount                  |                                                | Startap at Startastin                                                                                                                                                                                 |       |      | 10                         | μο                       |

| 801         | AArel <sub>Flex</sub> | Additional Relative Angular Error of FlexCount | referenced to output period T, see Figure 1 all resolutions all binary resolutions maximum resolution - 4                                                                                             | 0     |      | 25<br>0<br>25              | %<br>%<br>%              |

|             |                       |                                                | for RESIPO = 00 (8 bit interpolation): RESSUB = 0x01387 (resolution 5 000) RESSUB = 0x04E1F (resolution 20 000) RESSUB = 0x09C3F (resolution 40 000) RESSUB = 0x3FFFB (resolution 2 <sup>18</sup> -4) |       |      | 0.48<br>1.92<br>3.85<br>25 | %<br>%<br>%<br>%         |

| 802         | tp <sub>Flex</sub>    | Propagation Delay FlexCount                    | additional on top of tp <sub>lpo</sub> ()                                                                                                                                                             |       |      | 4/f <sub>oflex</sub>       |                          |

| 803         | f <sub>max</sub>      | Maximum Permissible Sin/Cos<br>Frequency       | OSZC = 10 RESIPO = 11 (5 bit interpolation) RESIPO = 10 (6 bit interpolation) RESIPO = 01 (7 bit interpolation) RESIPO = 00 (8 bit interpolation)                                                     |       |      | 250<br>226<br>113<br>56.5  | kHz<br>kHz<br>kHz<br>kHz |

| 804         | tst <sub>Flex</sub>   | Startup Time FlexCount                         | OSZC = 10, SELABS = 0, no illumination error, until POSOK = 1, incl. tst <sub>lpo</sub> RESIPO = 11 (5 bit interpolation): startup at 14500 rpm                                                       |       |      | 2.5                        | ms                       |

|             |                       |                                                | startup at standstill RESIPO = 10 (6 bit interpolation):                                                                                                                                              |       |      | 1.5                        | ms                       |

|             |                       |                                                | startup at 13200 rpm<br>startup at 12000 rpm<br>startup at standstill<br>RESIPO = 01 (7 bit interpolation):                                                                                           |       |      | 35<br>15<br>2.5            | ms<br>ms<br>ms           |

|             |                       |                                                | startup at 6600 rpm<br>startup at 6000 rpm<br>startup at standstill<br>RESIPO = 00 (8 bit interpolation):                                                                                             |       |      | 70<br>30<br>5              | ms<br>ms<br>ms           |

|             |                       |                                                | startup at 3300 rpm<br>startup at 3000 rpm<br>startup at standstill                                                                                                                                   |       |      | 140<br>60<br>10            | ms<br>ms<br>ms           |

|             |                       | puts INCA, INCB, INCZ                          |                                                                                                                                                                                                       |       |      | _                          |                          |

| 901         | Vs()hi                | Saturation Voltage hi                          | Vs()hi = VDD - V();<br>VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                                                                                                                       |       |      | 400                        | mV                       |

| 902         | lsc()hi               | Short-Circuit Current hi                       |                                                                                                                                                                                                       | -100  |      | -1.5                       | mA                       |

| 903         | Vs()lo                | Saturation Voltage lo                          | VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                                                                                                                                              |       |      | 400                        | mV                       |

| 904         | Isc()lo               | Short-Circuit Current lo                       |                                                                                                                                                                                                       | 1.5   |      | 100                        | mA                       |

| 905         | tr()                  | Rise Time                                      | CL = 30 pF, V(): $10\% \rightarrow 90\%$ VDD                                                                                                                                                          |       |      | 50                         | ns                       |

| 906         | tf()                  | Fall Time                                      | CL = 30 pF, V(): 90% → 10% VDD                                                                                                                                                                        |       |      | 50                         | ns                       |

Rev D1, Page 12/45

### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol          | Parameter                                              | Conditions                                                                      | Min.        | Тур.       | Max.      | Unit     |

|-------------|-----------------|--------------------------------------------------------|---------------------------------------------------------------------------------|-------------|------------|-----------|----------|

| SPI In      | terface SC      | K, CS, MISO, MOSI                                      |                                                                                 | Ш           | , ,,       | 1         |          |

| A01         | Vs()hi          | Saturation Voltage hi at MISO                          | Vs()hi = VDD - V();<br>VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA |             |            | 400       | mV       |

| A02         | lsc()hi         | Short-Circuit Current hi at MISO                       |                                                                                 | -100        |            | -1.5      | mA       |

| A03         | Vs()lo          | Saturation Voltage lo at MISO                          | VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                        |             |            | 400       | mV       |

| A04         | lsc()lo         | Short-Circuit Current lo at MISO                       |                                                                                 | 1.5         |            | 100       | mA       |

| A05         | fin()           | Permissible Clock Frequency at SCK                     |                                                                                 |             |            | 10        | MHz      |

| A06         | Vt()hi          | Threshold Voltage hi at SCK, CS, MOSI                  |                                                                                 |             |            | 2         | V        |

| A07         | Vt()lo          | Threshold Voltage lo at SCK, CS, MOSI                  |                                                                                 | 0.8         |            |           | V        |

| A08         | Vt()hys         | Hysteresis at SCK, CS, MOSI                            | Vt()hys = Vt()hi - Vt()lo                                                       | 40          | 100        |           | mV       |

| A09         | Ipu()           | Pull-Up Current at SCK, MOSI                           | V() = 0 VDD - 1 V;<br>VDD = 3 4 V<br>VDD = 4 5.5 V                              | -65<br>-120 | -25<br>-60 | -5<br>-10 | μA<br>μA |

| A10         | Vpu()           | Pull-Up Voltage at SCK, MOSI                           | Vpu() = VDD - V();<br>VDD = 3 4 V, I() = -3 μA<br>VDD = 4 5.5 V, I() = -5 μA    |             |            | 400       | mV       |

| A11         | lpd()           | Pull-Down Current at CS                                | V() = 1 V VDD;<br>VDD = 3 4 V<br>VDD = 4 5.5 V                                  | 5<br>8      | 25<br>60   | 80<br>150 | μA<br>μA |

| A12         | Vpd()           | Pull-Down Voltage at CS                                | VDD = 3 4 V, I() = 3 μA<br>VDD = 4 5.5 V, I() = 5 μA                            |             |            | 400       | mV       |

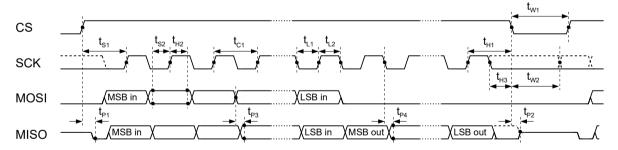

| A13         | t <sub>P2</sub> | Propagation Delay: MISO tristate after Falling Edge CS | CL = 10 pF, see Figure 2                                                        |             | 30         | 50        | ns       |

| A14         | t <sub>P4</sub> | Propagation Delay: MISO Stable after Clock Edge SCK    | CL = 10 pF, see Figure 2                                                        |             | 30         | 60        | ns       |

| Shift F     | Register CL     | LK, NSL, DOUT, DIN                                     |                                                                                 |             |            |           |          |

| B01         | Vs()hi          | Saturation Voltage hi at DOUT                          | Vs()hi = VDD - V();<br>VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA |             |            | 400       | mV       |

| B02         | Isc()hi         | Short-Circuit Current hi at DOUT                       |                                                                                 | -100        |            | -1.5      | mA       |

| B03         | Vs()lo          | Saturation Voltage Io at DOUT                          | VDD = 3 4 V, I() = 1.5 mA<br>VDD = 4 5.5 V, I() = 2.5 mA                        |             |            | 400       | mV       |

|             | lsc()lo         | Short-Circuit Current lo at DOUT                       |                                                                                 | 1.5         |            | 100       | mA       |

| B05         | fin()           | Permissible Clock Frequency at CLK                     |                                                                                 |             |            | 16        | MHz      |

| B06         | Vt()hi          | Threshold Voltage hi at CLK, NSL, DIN                  |                                                                                 |             |            | 2         | V        |

| B07         | Vt()lo          | Threshold Voltage lo at CLK, NSL, DIN                  |                                                                                 | 0.8         |            |           | V        |

| B08         | Vt()hys         | Hysteresis at CLK, NSL, DIN                            | Vt()hys = Vt()hi - Vt()lo                                                       | 40          | 100        |           | mV       |

| B09         | Ipu()           | Pull-Up Current at CLK, NSL                            | V() = 0 VDD - 1 V;<br>VDD = 3 4 V<br>VDD = 4 5.5 V                              | -65<br>-120 | -25<br>-60 | -5<br>-10 | μA<br>μA |

| B10         | Vpu()           | Pull-Up Voltage at CLK, NSL                            | Vpu() = VDD - V();<br>VDD = 3 4 V, I() = -3 μA<br>VDD = 4 5.5 V, I() = -5 μA    |             |            | 400       | mV       |

| B11         | lpd()           | Pull-Down Current at DIN                               | V() = 1 V VDD;<br>VDD = 3 4 V<br>VDD = 4 5.5 V                                  | 5<br>8      | 25<br>60   | 80<br>150 | μΑ<br>μΑ |

| B12         | Vpd()           | Pull-Down Voltage at DIN                               | VDD = 3 4 V, I() = 3 μA<br>VDD = 4 5.5 V, I() = 5 μA                            |             |            | 400       | mV       |

Rev D1, Page 13/45

### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol       | Parameter                                                     | Conditions                                                                       | Min.   | Тур.     | Max.      | Unit                     |

|-------------|--------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|--------|----------|-----------|--------------------------|

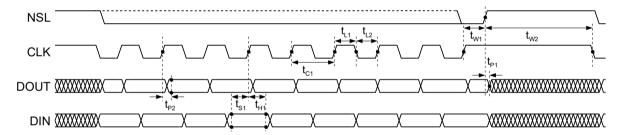

| B13         | tp3()        | Propagation Delay: DOUT Idle<br>State after rising Edge NSL   | CL = 10 pF, see Figure 3                                                         |        | 30       | 50        | ns                       |

| B14         | tp4()        | Propagation Delay: DOUT stable after Clock Edge CLK           | CL = 10 pF, see Figure 3                                                         |        | 30       | 60        | ns                       |

|             |              | Bit 015 (parameter EPG = 0x1) DIR, NSL, DIN, DOUT, CLK, GA, G | B, XJD, POK, INCZ, INCB, INCA, TPS, TI                                           | PC     |          |           |                          |

| C01         | Vs()hi       | Saturation Voltage hi                                         | Vs()hi = VDD - V();<br>VDD = 3 4 V, I() = 1.5 mA,<br>VDD = 4 5.5 V, I() = 2.5 mA |        |          | 400       | mV                       |

| C02         | Isc()hi      | Short-Circuit Current hi                                      |                                                                                  | -100   |          | -1.5      | mA                       |

| C03         | Vs()lo       | Saturation Voltage lo                                         | VDD = 3 4 V, I() = 1.5 mA,<br>VDD = 4 5.5 V, I() = 2.5 mA                        |        |          | 400       | mV                       |

| C04         | Isc()lo      | Short-Circuit Current lo                                      |                                                                                  | 1.5    |          | 100       | mA                       |

| C05         | tr()         | Rise Time                                                     | CL = 30 pF, V(): 10% → 90% VDD                                                   |        |          | 50        | ns                       |

| C06         | tf()         | Fall Time                                                     | CL = 30 pF, V(): 90% → 10% VDD                                                   |        |          | 50        | ns                       |

| Powe        | r-On-Reset   | POK                                                           | ,                                                                                |        | ,        |           |                          |

| D01         | Vs()hi       | Saturation Voltage hi                                         | Vs()hi = VDD - V();<br>VDD = 3 4 V, I() = 1.5 mA,<br>VDD = 4 5.5 V, I() = 2.5 mA |        |          | 400       | mV                       |

| D02         | Isc()hi      | Short-Circuit Current hi                                      |                                                                                  | -100   |          | -1.5      | mA                       |

| D03         | Vs()lo       | Saturation Voltage lo                                         | VDD = 3 4 V, I() = 1.5 mA,<br>VDD = 4 5.5 V, I() = 2.5 mA                        |        |          | 400       | mV                       |

| D04         | Isc()lo      | Short-Circuit Current lo                                      |                                                                                  | 1.5    |          | 100       | mA                       |

| D05         | VDDAon       | Turn-on Threshold VDDA,<br>Power-on-release                   | increasing voltage at VDDA;<br>POK: lo → hi                                      | 3.6    | 3.8      | 4.0       | V                        |

| D06         | VDDAoff      | Turn-off Threshold VDDA,<br>Power-down-reset                  | decreasing voltage at VDDA; EPG = 0, POK: hi $\rightarrow$ lo                    | 3.3    | 3.5      | 3.7       | V                        |

| D07         | VDDAhys      | Hysteresis                                                    | VDDAhys = VDDAon - VDDAoff                                                       | 0.2    | 0.3      |           | V                        |

| Code        | Inversion In | nput DIR                                                      |                                                                                  |        |          |           |                          |

| E01         | Vt()hi       | Threshold Voltage hi                                          |                                                                                  |        |          | 2         | V                        |

| E02         | Vt()lo       | Threshold Voltage lo                                          |                                                                                  | 0.8    |          |           | V                        |

| E03         | Vt()hys      | Hysteresis                                                    | Vt()hys = Vt()hi - Vt()lo                                                        | 40     | 100      |           | mV                       |

| E04         | lpd()        | Pull-Down Current                                             | V() = 1 V VDD;<br>VDD = 3 4 V<br>VDD = 4 5.5 V                                   | 5<br>8 | 25<br>60 | 80<br>150 | μ <b>Α</b><br>μ <b>Α</b> |

| E05         | Vpd()        | Pull-Down Voltage                                             | VDD = 3 4 V, I() = 3 μA<br>VDD = 4 5.5 V, I() = 5 μA                             |        |          | 400       | mV                       |

Rev D1, Page 14/45

### **ELECTRICAL CHARACTERISTICS**

| Item       | Symbol             | Parameter                         | Conditions                                       |                              |                              |                              |                          |

|------------|--------------------|-----------------------------------|--------------------------------------------------|------------------------------|------------------------------|------------------------------|--------------------------|

| No.        |                    |                                   |                                                  | Min.                         | Тур.                         | Max.                         |                          |

| Oscillator |                    |                                   |                                                  |                              |                              |                              |                          |

| F01        | f <sub>oipo</sub>  | Oscillator Frequency Interpolator | OSZC = 00<br>OSZC = 01<br>OSZC = 10<br>OSZC = 11 | 13.0<br>13.5<br>14.5<br>15.0 | 16.5<br>17.5<br>19.0<br>20.0 | 20.0<br>21.5<br>23.0<br>24.0 | MHz<br>MHz<br>MHz<br>MHz |

| F02        | f <sub>oflex</sub> | Oscillator Frequency FlexCount    | OSZC = 00<br>OSZC = 01<br>OSZC = 10<br>OSZC = 11 | 14.0<br>14.5<br>15.5<br>16.0 | 17.0<br>18.0<br>19.5<br>20.5 | 20.0<br>21.5<br>23.0<br>24.0 | MHz<br>MHz<br>MHz<br>MHz |

Figure 1: Definition of relative angle error

Rev D1, Page 15/45

### **OPERATING REQUIREMENTS: SPI Interface**

| Item | Symbol          | Parameter                                                            | Conditions                               |            |            | Unit |

|------|-----------------|----------------------------------------------------------------------|------------------------------------------|------------|------------|------|

| No.  |                 |                                                                      |                                          | Min.       | Max.       |      |

| 1001 | t <sub>C1</sub> | Permissible Clock Period                                             | see Elec. Char. No.: A05                 | 1/fin()    |            |      |

| 1002 | t <sub>W1</sub> | Wait Time: between CS hi $\rightarrow$ lo and CS lo $\rightarrow$ hi |                                          | 500        |            | ns   |

| 1003 | t <sub>S1</sub> | Setup Time:<br>CS hi before SCK lo → hi                              |                                          | 50         |            | ns   |

| 1004 | t <sub>P1</sub> | Propagation Delay:<br>MISO stable after CS lo → hi                   | CL = 10 pF                               |            | 50         | ns   |

| 1005 | t <sub>P2</sub> | Propagation Delay:<br>MISO tristate after CS hi → lo                 |                                          |            | . No.: A13 |      |

| 1006 | t <sub>H1</sub> | Hold Time:<br>CS hi after SCK lo → hi                                | valid for SPI mode 3                     | 50         |            | ns   |

| 1007 | t <sub>S2</sub> | Setup Time:<br>MOSI stable before SCK lo → hi                        |                                          | 50         |            | ns   |

| 1008 | t <sub>H2</sub> | Hold Time:<br>MOSI stable after SCK lo → hi                          |                                          | 50         |            | ns   |

| 1009 | t <sub>P3</sub> | Propagation Delay:<br>MISO stable after MOSI change                  | mode: repeating MOSI on MISO, CL = 10 pF |            | 50         | ns   |

| I010 | t <sub>P4</sub> | Propagation Delay:<br>MISO stable after clock edge SCK               | mode: sending data MISO, CL = 10 pF      | Elec. Char | . No.: A14 |      |

| 1011 | t <sub>W2</sub> | Wait Time:<br>SCK stable after CS hi → lo                            |                                          | 500        |            | ns   |

| 1012 | t <sub>H3</sub> | Hold Time:<br>CS hi after SCK hi → lo                                | valid for SPI mode 0                     | 50         |            | ns   |

| I013 | t <sub>L1</sub> | Clock Signal lo Level Duration                                       |                                          | 50         |            | ns   |

| 1014 | $t_{L2}$        | Clock Signal hi Level Duration                                       |                                          | 50         |            | ns   |

Figure 2: SPI interface timing

Rev D1, Page 16/45

### **OPERATING REQUIREMENTS: Shift Register**

| Item | Symbol          | Parameter                                                                     | Conditions               |                  | Unit       |

|------|-----------------|-------------------------------------------------------------------------------|--------------------------|------------------|------------|

| No.  |                 |                                                                               |                          | Min. Max         | <b>κ</b> . |

| I101 | t <sub>C1</sub> | Permissible Clock Period                                                      | see Elec. Char. No.: B05 | 1/fin()          |            |

| l102 | t <sub>W1</sub> | Wait Time Load Signal: NSL low after CLK lo $\rightarrow$ hi                  |                          | 30               | ns         |

| I103 | t <sub>P1</sub> | Propagation Delay:<br>DOUT (idle state) after NSL lo → hi                     | CL = 10 pF               | Elec. Char. No.: | B13        |

| l104 | t <sub>P2</sub> | Propagation Delay:<br>DOUT stable after CLK lo → hi                           | CL = 10 pF               | Elec. Char. No.: | B14        |

| I105 | t <sub>S1</sub> | Setup Time: DIN stable before CLK lo $\rightarrow$ hi                         |                          | 30               | ns         |

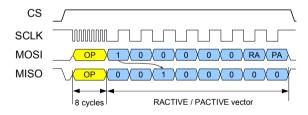

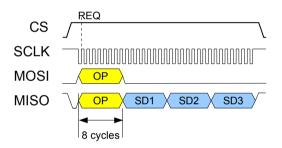

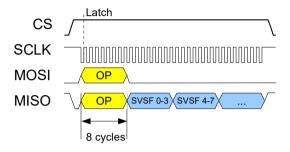

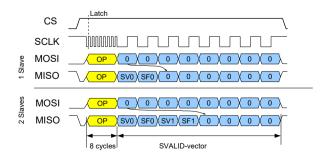

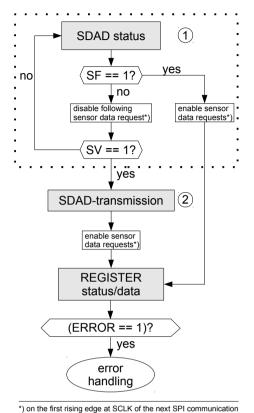

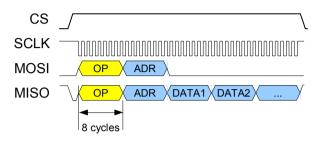

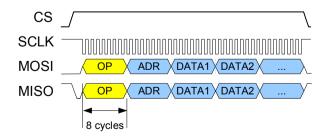

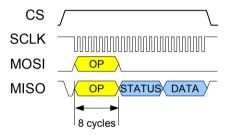

| I106 | t <sub>H1</sub> | Hold Time:<br>DIN stable after CLK lo → hi                                    |                          | 30               | ns         |